|

CZT & ASIC development

1. ProtoEXIST1

The principal technology challenge is the development of the very

large array of CZT imaging detectors. The small pixels on a single CZT

crystal allow more efficient detector and readout connections to a single

multi-pixel readout ASIC (application specific integrated circuit), which

provides charge preamp, shaping and peak detect on each pixel above a

programmable threshold.

The CZT-ASIC readout must allow for an inter-connect and packaging

system that permits tiling of the CZT-ASIC modules in a semi-infinite

detector plane without (significant) gaps to achieve maximum packing

efficiency without dead spaces on a motherboard for interface to a

digital data system.

Over the past year of our current SRT program, we have carried out an

extensive test program for the detector and RADNET ASIC module for

the prototype module of 2 x 2 CZT crystals and ASICS for

ProtoEXIST1.

Over the past year of our current SRT program, we have carried out an

extensive test program for the detector and RADNET ASIC module for

the prototype module of 2 x 2 CZT crystals and ASICS for

ProtoEXIST1.

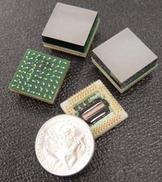

Many of the features of this ASIC (approximate gain, and particularly

its multi-pixel readout capability) are appropriate for ProtoEXIST1.

Thus, we employ the RADNET detector packaging architecture

to be fundamental detector module - a Detector

Crystal Module (DCM) consisting of a 20 x 20 x 5mm CZT crystal with 8

x 8 pixel anodes connected through an Interposer Board (IPB) to the

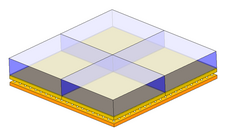

ASIC underneath the IPB. The figure shows views of the DCM (yellow - IPB

and pink - RADNET ASIC), and the photo shows the actual modules.

Many of the features of this ASIC (approximate gain, and particularly

its multi-pixel readout capability) are appropriate for ProtoEXIST1.

Thus, we employ the RADNET detector packaging architecture

to be fundamental detector module - a Detector

Crystal Module (DCM) consisting of a 20 x 20 x 5mm CZT crystal with 8

x 8 pixel anodes connected through an Interposer Board (IPB) to the

ASIC underneath the IPB. The figure shows views of the DCM (yellow - IPB

and pink - RADNET ASIC), and the photo shows the actual modules.

This has been in close collaboration with LLNL and

Caltech, who have developed a 64 channel ASIC derived from the

Caltech-HEFT design (Cook et al 1998) that was optimized for higher

energy range (~100-1000 keV) for Homeland Security application as a

cellphone-based radiation detector (RADNET).

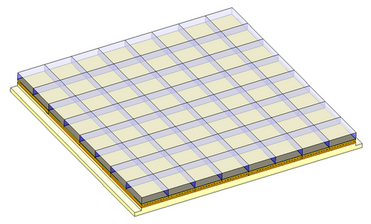

The DCM mounts to a motherboard via a pingrid

array and 4 such DCMs will be mounted to a

common Detector Crystal Array (DCA) board containing the FPGA to

control and readout the 4 ASICs.

We combine 4 x 4 DCAs onto a Detector Module (DM,

256 cm2) and 4 DMs complete the detector plane

(10242cm) for ProtoEXIST1.

This has been in close collaboration with LLNL and

Caltech, who have developed a 64 channel ASIC derived from the

Caltech-HEFT design (Cook et al 1998) that was optimized for higher

energy range (~100-1000 keV) for Homeland Security application as a

cellphone-based radiation detector (RADNET).

The DCM mounts to a motherboard via a pingrid

array and 4 such DCMs will be mounted to a

common Detector Crystal Array (DCA) board containing the FPGA to

control and readout the 4 ASICs.

We combine 4 x 4 DCAs onto a Detector Module (DM,

256 cm2) and 4 DMs complete the detector plane

(10242cm) for ProtoEXIST1.

2. ProtoEXIST2

The desired 5' resolution for the primary high energy

telescopes on EXIST, and the constraints on mask-detector focal length

as 1.5m, require 1.25mm pixels for Nyquist sampling of the mask

shadow. Thus the transition to ProtoEXIST2 is a factor of 2

reduction in CZT pixel size and corresponding factor of 4 in ASIC

pixel number and corresponding increased complexity of connecting the

ASIC to the CZT through the IPB. The desired smaller pixels are more

subject to charge spreading, especially at higher energies, so

multipixel events are more likely. Hence the need for a higher

resolution, multipixel (at least peak plus neighbors, but commandable)

CZT-ASIC combination.

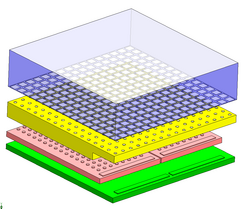

Significant work has already been done on the design concept for this

ASIC during our current SRT grant. However, final layout of this ASIC has

not yet begun due to uncertainty about the best way to couple the ASIC

to the CZT: either with an IPB (as for RADNET and ProtoEXIST1) or with

direct-bonding as for HEFT. The figure shows packaging conceprt using

an IPB for "de-magnification" of pixel pitch from the CZT (1.25mm pitch)

to an ASIC array input (0.9 mm pitch).

The desired 5' resolution for the primary high energy

telescopes on EXIST, and the constraints on mask-detector focal length

as 1.5m, require 1.25mm pixels for Nyquist sampling of the mask

shadow. Thus the transition to ProtoEXIST2 is a factor of 2

reduction in CZT pixel size and corresponding factor of 4 in ASIC

pixel number and corresponding increased complexity of connecting the

ASIC to the CZT through the IPB. The desired smaller pixels are more

subject to charge spreading, especially at higher energies, so

multipixel events are more likely. Hence the need for a higher

resolution, multipixel (at least peak plus neighbors, but commandable)

CZT-ASIC combination.

Significant work has already been done on the design concept for this

ASIC during our current SRT grant. However, final layout of this ASIC has

not yet begun due to uncertainty about the best way to couple the ASIC

to the CZT: either with an IPB (as for RADNET and ProtoEXIST1) or with

direct-bonding as for HEFT. The figure shows packaging conceprt using

an IPB for "de-magnification" of pixel pitch from the CZT (1.25mm pitch)

to an ASIC array input (0.9 mm pitch).

|